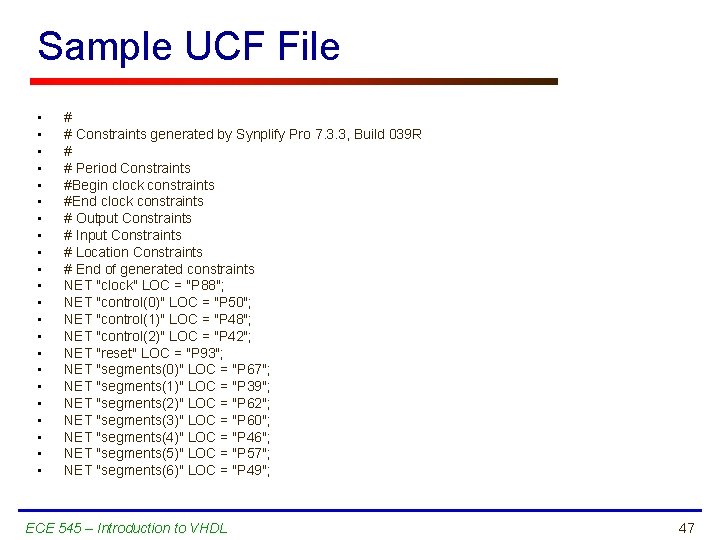

Now the important part: when I synthesize this with Synplify pro it correctly detects the primary clock but then detects the "slow clock" module as a clock and gets the timing wrong. That output then goes to a blinky led module that counts up infinitely and reveals the state of the 8 bit counter on some LEDs. That clock then connects to a module that increments a counter and flips an output register every 100000 cycles. What I did was instantiate the internal oscillator block (OSCH) for the MachXO3 and defparam'd the frequency to the minimum of 2.08 in Verilog.

I'm fiddling with the options using a trivial blinky led design using two counters and 8 LEDs. Right now I'm trying to get a handle on the best way to set clock speed and timing constraints, specifically using Synplify Pro.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed